The Deep Learning Inference Acceleration Blog Series — Part 2- Hardware | by Amnon Geifman | Towards Data Science

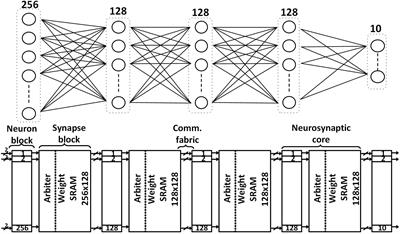

Frontiers | Always-On Sub-Microwatt Spiking Neural Network Based on Spike-Driven Clock- and Power-Gating for an Ultra-Low-Power Intelligent Device

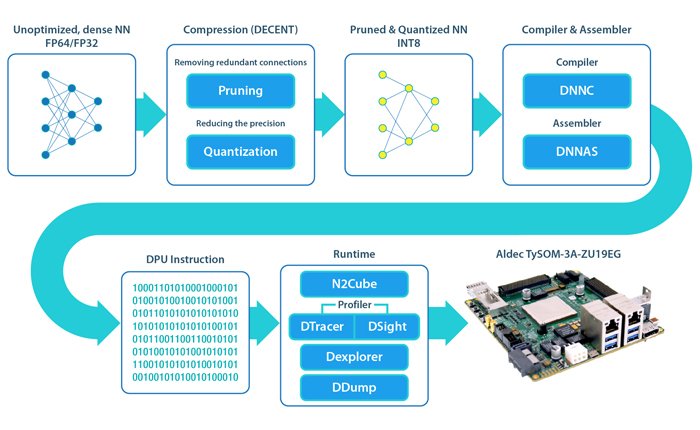

Blog: Aldec Blog - How to develop high-performance deep neural network object detection/recognition applications for FPGA-based edge devices - FirstEDA